英语原文共 4 页,剩余内容已隐藏,支付完成后下载完整资料

窗体顶端

窗体顶端

窗体顶端

基于FPGA的数字频率计的设计与实现

重庆电子工程学院,重庆,401331

关键词:FPGA,数字频率计,设计与实现

摘要

EDA技术的发展改变了传统的电子设计方法,现在已广泛应用于大型FPGA等可编程逻辑器件,使电子设计和软件编程变得简单快捷。电子设计技术的进步,也改变了传统的频率计设计。它不仅运用常规频率测量方法所采用的模拟电路的频率特性进行频率测量,还采用了数字脉冲计数的频率测量方法。随着数字电路的发展,各种数字频率测量方法不断改进,测量精度不断提高,测量速度越来越快,脉冲计数技术测量方法应运而生。本文分析了直接频率测量方法测量周期频率,并说明了产生plusmn;1计数误差的原因。

介绍

频率计设计技术与电子电路技术的发展逐渐前进,早期频率计设计采用分立元件,设计时间长,稳定性差,成品体积大,功耗高。数字电子技术和集成电路使数字频率计,数字频率计电路和微控制器单元可用于设计和实现。与分立的频率计相比,一个数字频率计提高了稳定性,减小了音量,但仍有电路复杂,设计周期长等缺点。数字频率计的测量范围受到了限制,测量不同频率的信号被设计为电路的一部分,灵活性差。 20世纪,微电子技术的发展进步促进FPGA系列中代表应用可编程逻辑器件变得越来越普遍。可编程逻辑器件编程通用集成电路集成到单个硅片上的尺寸小,呈指数级减小电路的尺寸,并且因为走线短路,减少干扰并增加系统可靠性。因为这样的设备可以通过软件编程及其重构硬件的结构和工作方法,如硬件设计软件设计方便,在数字电路系统的设计中带来了很大的灵活性。随着可编程逻辑器件的集成不断扩大,计算机辅助设计技术能力不断完善和提升,EDA现代电子系统设计领域诞生了。

频率测量技术研究

目前,用于测量测量频率精度的许多方法取决于测量频率范围和测量对象的频率特性。因为时钟频率不仅取决于其精度所使用的标准,也取决于所使用的测量仪器和方法。 接下来,介绍几种类型常用的是频率测量方法:直读频率测量, 直接阅读测量频率的桥梁频率测量方法,谐振频率测量方法,频率 - 电压转换频率测量法。

频率测量方法比较的是标准频率fc和测量频率fx,当标准频率调整到与测量频率相等时表示零点,即测量频率标准值频率值。测量频率的比较可以分为拍频测量和差频测量频率模型。前者是要衡量的频率信号和标准频率信号叠加在线性元件上产生a拍频后者是测量频率信号和标准频率信号非线性混合元件。目前拍频的绝对误差测量频率为约十分之几赫兹,差频测量误差的频率可以是数量级优于10-5,最小可检测信号电平为0.1mu;V〜1mu;V。差分频率法在常规情况下很少使用。

测量频率计数方法常用于数字频率计。 计数是周期信号计数的每单位时间的数量。计数频率测量的精度取决于精度和误差计数参考时间。 该设计采用计数频率测量,符合以下符号频率测量和频率测量原理基于几种方法计数方法进行详细分析。

FPGA结构和工作原理

FPGA是现场可编程逻辑阵列(Field Programmable Gate Array,现场可编程门阵列)缩写。 它是CPLD(复杂可编程逻辑器件,复杂可编程逻辑器件)用于一类大型可编程逻辑器件。

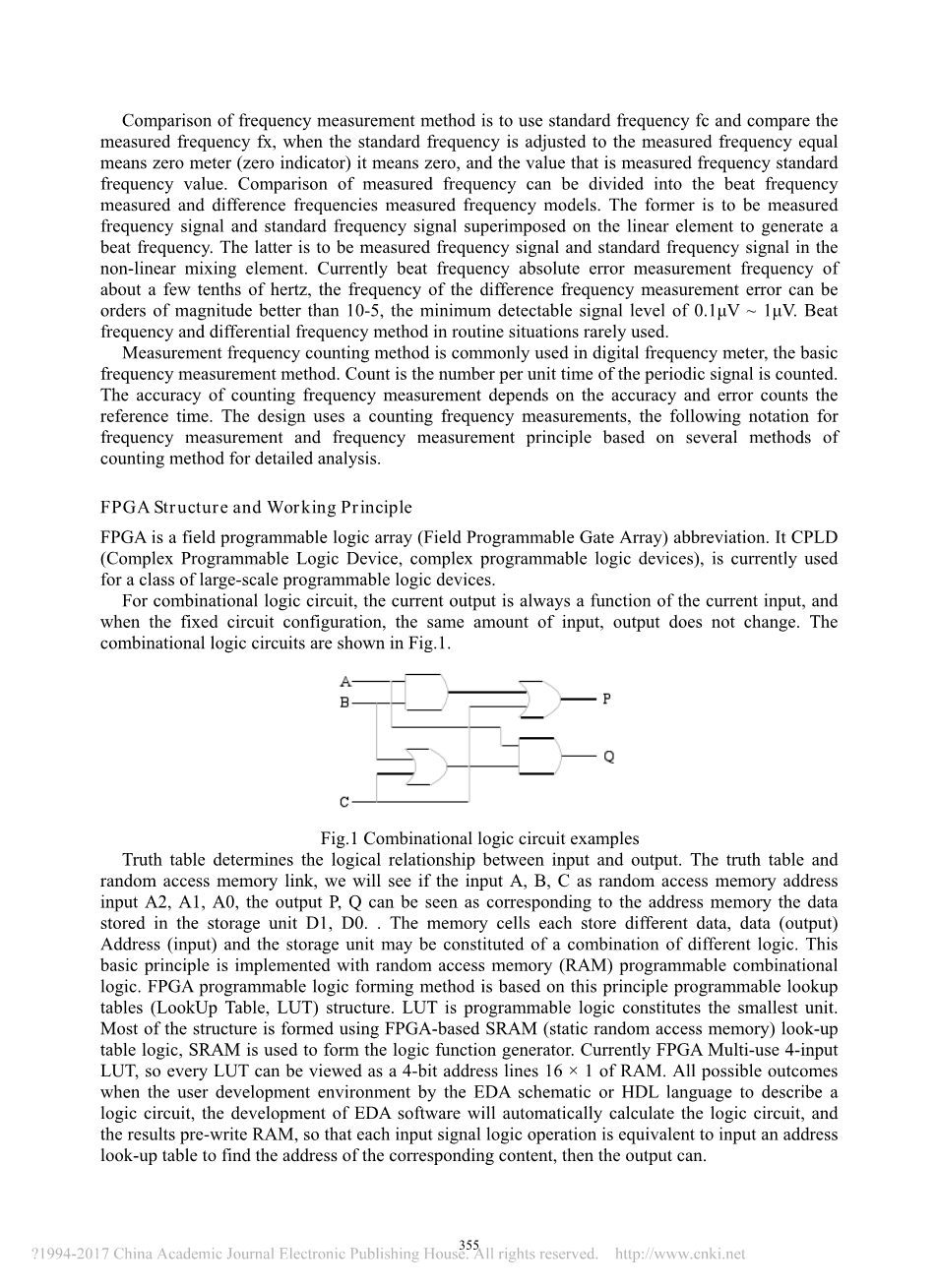

对于组合逻辑电路,电流输出始终是当前输入的函数当固定电路配置时,输入量相同,输出不变。该组合逻辑电路如图1所示。

图1组合逻辑电路示例

真值表确定输入和输出之间的逻辑关系。真相表和随机存取存储器链接,我们将看到输入A,B,C是否随机存取存储器地址输入A2,A1,A0,输出P,Q可以看作对应于地址存储器的数据存储在存储单元D1,D0中。 存储单元每个存储不同的数据,数据(输出)地址(输入)和存储单元可以由不同逻辑的组合构成。这个基本原理是用随机存取存储器(RAM)实现的可编程组合逻辑。 FPGA可编程逻辑形成方法是基于这个原理可编程查找表(LookUp Table,LUT)结构。 LUT是可编程逻辑构成最小单位。大多数结构是使用基于FPGA的SRAM(静态随机存取存储器)查找形成的表逻辑,SRAM用于形成逻辑函数发生器。目前FPGA多用4输入LUT,因此每个LUT可以被视为RAM的4位地址线16times;1。所有可能的结果当用户开发环境由EDA原理图或HDL语言描述一个逻辑电路,EDA软件的开发将自动计算逻辑电路,而结果预写RAM,使每个输入信号的逻辑运算相当于输入一个地址查找表找到相应内容的地址,然后输出即可。

基于FPGA的频率计设计

频率测量和显示整个频率计控制模块是核心模块对于全数字电路,采用FPGA器件采用VHDL编程实现。频率测量部分采用多段同步测频方式实现等精度频率测量,测量精度和参考频率信号频率,精度和相关门开启时间,以及信号的频率独立,实现了广泛的同等精度的频率测量。信号来自信号整形模块的频率测量部分,作为所有脉冲计数频率测量只能接收脉冲信号,信号必须形成一个脉冲信号信号与频率。参考频率测量部分(时钟)信号产生“参考频率(时钟)信号模块”。门信号发生器预置门信号,因为它是编程,长可以编程修改所有打开的门信号。运算符按公式fx =(Nx / Nc)bull;fc计算测量信号的频率值,乘法运算符并且分工操作包括两个操作。显示控制部分包括BCD码转换器,解码器锁存两个子模块。频率算子以二进制形式获得以十进制形式显示,并且必须是BCD代码转换器,以BCD码的形式为十进制。

频率表显示部分采用7段,所以解码器,锁存器完成显示解码器BCD码,还具有存储解码功能。

该模块使用标准产生参考频率信号频率测量时钟脉冲信号,也称为时钟信号模块。 该模块使用晶体振荡器相应的硬件电路产生标准时钟信号,除了提供一个参考时钟信号频率信号频率测量第1部分的计数器,也是向门信号发生器提供定时时钟信号。信号的形式根据频率测量后的脉冲数可以变化只接受脉冲频率信号,该信号必须被成形以形成测量信号脉冲信号频率到频率值测量。 频率响应特性信号整形模块还可以确定上位机的频率测量频率范围频率。

为了简化设计,频率计仅显示测量的整数部分信号频率值。 显示模块使用六个七段LED显示屏。 因为七段解码器,锁存电路具有频率测量显示模块设计完成后,六个数字管直接将FPGA引脚输出到相应的输出端,也可以考虑数字驱动管的问题。

电源模块为整个电压表模块提供了所需的标准。电源模块220V交流电源输入后,变压器整流器,调压器通过输出系统所需的直流电压稳定。

功率模块的频率计设计与实现

频率测量和显示控制模块设计采用自顶向下的设计方法。 第一,该模块根据功能分为几个子模块,然后使用VHDL,最后通过顶层设计文件将每个子模块组合到一起完整的频率测量和显示控制功能。

参考频率信号是根据频率进行测量的参考频率信号也用作定时时钟信号乘法器,分频器,BCD码转换器等。本设计中使用的Cyclone系列FPGA器件高性能嵌入式模拟锁相环(DPLL性能远胜于此)锁相环(PLL)可以与时钟信号输入同步,输入时钟为PLL参考实现,和输入时钟倍频器或做1到32分频。与外部时钟直接相比,内部时钟该芯片可以减少时钟延迟和时钟失真,减少芯片干扰,还可以提高设置时间和保持时钟。

虽然测量的信号是周期性信号,但其形式可能会变化。 但频率测量信号模块只能以脉冲的形式进行测量,所以在测量之前对测量信号整形,将不同形式的信号组织成周期脉冲信号。

频率测量系统由不同的芯片组成,每个芯片需要电源电压有不同的要求,所以要求电源模块提供多个电压值。 Altera公司的EP1C3T144C8芯片电压采用了FPGA器件器件为1.5V,I / O电压为3.3V,FPGA需要提供 1.5V和 3.3V双电压;反相振荡电路74LS04器件需要 5V电压; LM361标准电压Vcc是 5V,V 和V-电压范围宽,V 需要5V〜15V,-V-在-6V〜-15V之间。

频率值的设计由六个七段LED显示屏测量。 自从锁存功能显示解码器和FPGA设计中数字值的解码已经完成后,所以FPGA输出可以直接访问输入数字管显示频率值。然而,由于FPGA驱动能力有限,它只说了理论上的观点,实际上应用,还可以访问数字前管驱动电路,这里我们使用ULN2003作为数字管驱动器。

结论

频率计是常用的电子测量设备之一。随着电子技术的发展,设计方法的频率计正在逐步走向前列。离散件从早期到集成电路,LSI,这个过程有适当的设计功能部件要完成。随着电子设计的发展,大规模,超大规模可编程逻辑器件的出现,电子电路包括频率计设计变得更加简单方便,而且在不改变硬件结构的基础上,可以根据设计改变要求设计,不同功能甚至完整的系统具有相同的硬件电路设计。基于对频率分析和比较的几种常用方法测量方法,同步频率测量方法根据设计需要使用多周期频率计设计。由于EDA设计技术的大部分设计在计算机上完成了工作,逻辑仿真也在计算机中完成了。

参考文献

[1] W. Zhou. Systematic Reseach on High-Accuracy Frequency Measurements and Control.

Shizuoka University.Doctor Dissertation, 2000:15-24,90-96

[2] M.A.A .Sour, H.I.Saleh. An FPGA Inplem Entation Guide for Some Different Types

Ofserial-Parallel Multiplier Structures. Microelectronics Fournal, 2000, 31(3):161-168

[3] W.Zhou. Some New Method for Precision Time Interval Measurement. Proceedings Of The1977

Ieee International Frequency Control Symposium, 1997,418-421

[4] R.A.James, F. Gallgray. Vhdl Design Expression and Synthesis of Vhdl. Cambridge: Harvard

University Press, 2001

[5] C.Altera. Configuration Devices For Sram-Based Lut Devices. 2002.

[6] F.W.John. Digital Design Principles And Practices,2001.

[7] M.M.Mano. Digital Design, 3rd Ed. Prentice Hall Usa,2002.

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[28336],资料为PDF文档或Word文档,PDF文档可免费转换为Word