英语原文共 7 页,剩余内容已隐藏,支付完成后下载完整资料

具有改进电热性能的创新SiGe HBT拓扑结构

摘要:为了改善硅锗异质结双极晶体管的安全工作特性,本文研究了在最先进的双晶半导体工艺中设计和制造的硅锗异质结双极晶体管的替代拓扑结构。对各种结构的电热性能进行了分析比较,并对其优缺点进行了详细讨论。研究中的测试结构在发射指状布局和后端金属堆叠方面有所不同。结果表明,手指长度不均匀的多指晶体管结构具有较宽的深沟槽包围面积和较高的金属化堆叠,热性能得到改善。因此,在不降低射频性能的前提下,可以扩大多指晶体管的安全工作范围。

关键词:线后端(BEOL),深沟槽,发射极布局,多指晶体管,安全工作区(SOA),硅锗异质结双极晶体管(SiGe HBTs),热阻。

I.介绍

最先进的硅锗异质结双极晶体管(SiGe HBTs)对毫米波的应用很有吸引力,在亚太赫兹范围内[1]、[2]具有良好的性能。SiGe技术仍可优先于其他大功率应用技术,特别是其良好的性能和较低的成本,是[3]-[5]大批量生产市场的良好选择。由于计算机辅助设计(TCAD)技术的不断支持,紧凑的建模和表征活动[1],[6],[7],使得这一技术有希望的过程发展成为可能。

对于这种技术,多指晶体管结构通常是首选的,因为在各种优点中,与具有相同发射极面积的单个HBT相比,多指晶体管具有更好的电流处理能力和更好的散热。因此,它们是在高频传输高功率的首选。然而,在这些装置中,

静态[8]、[9]和动态[10]运行时,手指间存在热耦合效应,导致结构内部热分布不平衡,中指部温度达到最高[11]。由于这些元件的正电热反馈,手指越热,电流越大,形成电热回路(加上冲击电离效应),性能下降,最终导致不稳定和设备故障。不稳定性受到集电极电流在共发射极结构中偏压和基极电压(VBE)[12] -[14]激励时的回飞行为的限制。

提高多指高温超导热稳定性的可能途径之一是使用压载电阻[15],但这种方法会导致输出功率的降低和晶体管的功率增加效率的降低。替代技术,旨在更好的热稳定性,避免热点的形成提出了在文献[16],[17]和基本主张增加中央发射器的手指之间的间距减少相互热耦合或减少中央手指的长度,收益率较低的热量生成。

近年来在[18]-[21]等工程中应用了开发后端金属化(BEOL)的原理,证明了最先进的技术对SiGe HBTs的热行为有显著的影响。在这些工作中,通过TCAD模拟或分析建模,分析了BEOL对高温超导热性能的影响。关于这些BEOL栈的优化,文献中提供的信息有限。以[22]为例,提出了一些新颖的测试结构来研究金属假人产生的应变对晶体管基带隙的影响。金属堆叠放置在晶体管的有源部分之上,其结果是IC的显着增量以及更高的传输频率(fT)。这种改进的电气行为是由基地能带结构的变化引起的,而没有合理的热性能的改善报告,可能由于金属假人不通过连接的发射极接触,而达到高温设备操作时高功率耗散[23]。

本文分别研究了两种改进电热性能的方法,并对一定数量的测试结构进行了电热表征。我们从本质上提出了一些专用的测试结构,其中晶体管在作用于布局的水平面上或在垂直平面上进行修改,添加金属假人。

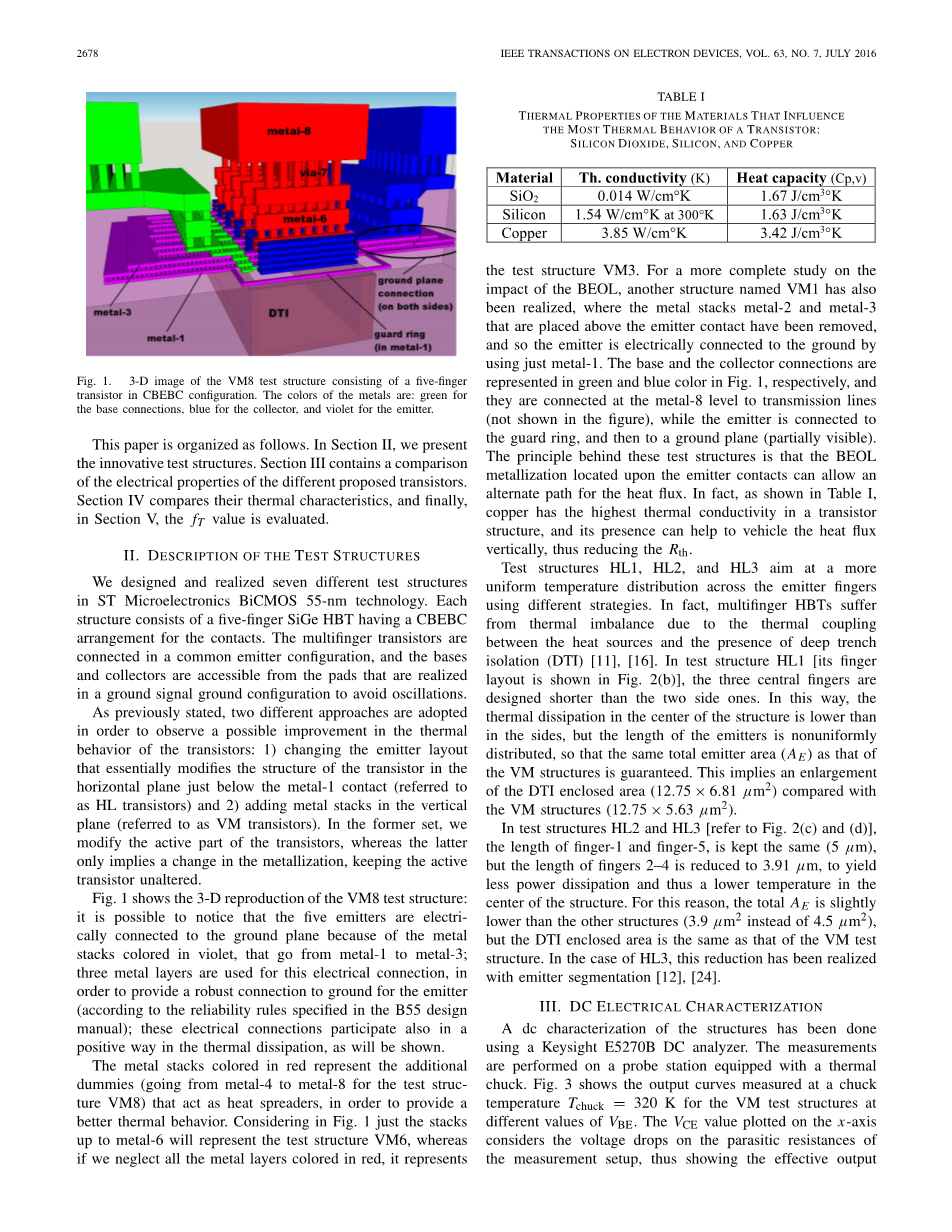

图1VM8测试结构的三维图像,由CBEBC配置的五指晶体管组成。金属的颜色是:绿色为基极连接,蓝色为集电极,紫色为发射极。

本文组织如下。在第二部分,我们提出了创新的测试结构。第三节比较了不同晶体管的电特性。第四节比较了它们的热特性,最后在第五节对fT值进行了评价。

II. 测试结构的描述

我们在ST微电子BiCMOS 55-nm技术中设计并实现了7种不同的测试结构。每个结构由一个五指SiGe HBT组成,该HBT对触点具有CBEBC安排。所述多指晶体管以共同的发射极结构连接,所述基极和集电极可从所述衬垫上获得,衬垫在地信号地结构中实现,以避免振荡。

如前所述,采用两种不同的方法来观察可能提高晶体管的热行为:1)改变发射器的结构布局,本质上修改晶体管在水平面以下metal-1接触(称为HL晶体管)和2)添加金属栈在垂直平面上(称为VM晶体管)。在前一组中,我们对晶体管的有源部分进行了修改,而后一组只意味着金属化的改变,使有源晶体管保持不变。

如图1所示为VM8测试结构的三维再现图:可以看到,由于金属-1到金属-3呈紫色的金属堆叠,五个发射体与地平面电连接;该电气连接采用三层金属层,为发射极提供与地面的可靠连接(根据B55设计手册规定的可靠性规则);这些电气连接也以一种积极的方式参与散热,这将显示出来。

用红色表示的金属堆代表额外的假人(在VM8测试结构中,从metal-4到metal-8),这些假人充当散热片,以便提供更好的散热性能。考虑到在图1中,只有metal-6之前的堆栈表示测试结构VM6,而如果我们忽略所有红色的金属层,它表示测试结构VM3。

表1

影响晶体管热行为的材料的热特性:

二氧化硅,硅和铜

为了更全面地研究BEOL的影响,还实现了另一种名为VM1的结构,其中,放置在发射极接触面上方的金属堆叠金属-2和金属-3被移除,因此发射极通过使用金属-1与地面电连接。底座和集电极连接分别用图1中的绿色和蓝色表示,金属8级连接到传输线(图中未显示),发射器连接到保护环,然后连接到接地平面(部分可见)。这些测试结构背后的原理是,位于发射极接点上的BEOL金属化可以允许热通量的另一条路径。实际上,如表1所示,在晶体管结构中,铜的导热系数最高,它的存在有助于垂直地传递热流,从而降低了Rth。

测试结构HL1、HL2和HL3的目标是使用不同的策略在发射器手指上实现更均匀的温度分布。事实上,由于热源之间的热耦合以及深沟隔离(DTI)[11]、[16]的存在,多指HBTs存在热不平衡。在测试结构HL1[手指布局如图2(b)所示]中,三个中心手指的设计比两个侧边手指短。这样,结构中心的热耗散低于两侧,但发射器的长度是非均匀分布的,从而保证了与VM结构相同的总发射器面积(AE)。这意味着一个扩大的DTI封闭区(12.75times;6.81mu;m2)与VM结构(12.75times;5.63mu;m2)。

在测试结构HL2和HL3(参考图2(c)和(d)),图一和finger-5的长度,保持相同的(5mu;m),但手指的长度2 - 4是减少到3.91mu;m,功耗就越低,因此较低的温度结构的中心。出于这个原因,总AE略低于其他结构(3.9mu;m2代替4.5mu;22),但DTI封闭面积是一样的VM的测试结构。在HL3的情况下,这种减少是通过发射器分割[12],[24]来实现的。

III. 直流电特性

利用Keysight E5270B直流分析仪对结构进行了直流表征。测量是在一个装有热卡盘的探测站上进行的。图3为不同VBE值下VM测试结构在卡盘温度Tchuck = 320k下测量的输出曲线。绘制在x轴上的VCE值考虑了测量装置寄生电阻上的电压降,从而显示了有效输出

图2指布局的测试结构。DTI以橙色显示,而绘制的五个发射极窗口以蓝色显示。(a) VM测试结构。DTI封闭区域= 71.78mu;m2 。AE = 4.5mu;m2 。(b) HL1测试结构= 86.83mu;m2 。AE = 4.5mu;m2 。(c) HL2测试结构= 71.78mu;m2 。AE = 3.91mu;m2 。(d) HL3测试结构。= 71.78mu;m2 。AE = 3.91mu;m2 。

图3晶体管虚拟机输出特性的比较。VBE从0.825 V扫到0.9 V。子图显示了VBE = 0.875 V时,中等VCE范围内机械应力的影响

晶体管的特性。很明显,经过一定的功耗(Pdiss)后,由于每个测试结构的热阻不同,晶体管的性能开始有所不同。事实上,一旦一个相对较高的值达到Pdiss(在该地区的情节突出显示虚线圆,总Pdiss估计范围在50到190兆瓦),结温的不同的值(Tj),根据组件的热阻。一旦Tj足够高,晶体管的电特性就会受到更大强度的影响。

图4用于测试结构HL的集电极电流密度JC。VM3用作参考。VBE从0.825 V扫到0.9 V

当驱动的基础电压(如在我们的测量设置),晶体管的IC值呈现正的电热反馈,因此当出现更强烈的自热效应时,IC值会增加。如果晶体管的Rth值很高,这种现象当然会更严重。IC变化最大的VBE值为VBE=0.875V;当基发射体电压进一步增大时,雪崩倍增、冲击电离等效应相对于自热效应表现出明显的优势,不同测试结构间观察到的IC变化较小。对于高功耗区域的IC,我们得到的结果显示,从结构VM1过渡到结构VM8,在偏置点VBE=0.875V和VCE=1.42V时,IC下降了12%左右。与VM1相比,该集成电路可归因为晶体管VM8的Rth较低。在相同的偏置点,从VM1切换到VM8, IB反而减少了51%,导致直流电流增益整体增加了34%左右。当从VM6传递到VM8时,没有发现明显的IC变化。

另一方面,我们可以注意到在图3的次要情节,在该地区在低输出曲线的VCE(功耗很低),测试结构VM8下水道IC略高于VM1(增长4.5%是观察到VBE=0.9V和VCE=0.6V)。这是由于金属假人的机械应变效应导致HBT的能带结构的变化,如[22]所述。

对于HL测试结构,我们将考虑两个不同AE值的晶体管;因此,在图4中,我们将测量到的电流密度JC作为VCE的函数进行比较(还添加了参考结构VM3的结果)。从图中可以看出,对于Pd最大值对应的偏置点(VCE=1.42V, VBE=0.875V),JC从结构VM3过渡到HL1时下降18%。在高功率密度下,结构HL2和HL3的JC更低,因此,从电热角度来看,它们似乎更受青睐,尽管与VM3相比,它们的AE更低,因此Rth应该更高。这方面将在第四节中进一步讨论。

图5测量的输出电导作为功能的VCE的结构VM。VBE = 0.875 V

输出电导的分析如图5所示,图中绘制了输出电导与实测IC的对比图。我们可以推断,在高功耗情况下,随着在发射器上方的假人中添加更多的金属堆栈,输出电导的值会更低,从而确保安全操作区域(SOA)规范的行为得到改进。事实上,在晶体管必须在其SOA边缘附近区域运行的应用程序中,可以选择固定输出电导的最大可接受值(对应于输出曲线中IC的最大斜率)。由图5不难看出,一旦固定了某个gout_MAX,我们增加的金属堆叠越多,就越有可能在晶体管上增加一个额外的VCE(或相当于一个额外的IC)。

例如,如果我们修正gout_MAX = 270mS,我们可以应用到晶体管上的VCE的最大值为VM1的1.35 V和VM8结构的1.43 V,这允许大约6%的额外VCE。相反,如果我们将gout绘制为IC的函数,并对gout_MAX固定相同的值,那么在测试结构VM8的HBT中,与VM1相比,可以多流大约10ma的电流(对应增加12%)。

HL结构和参考结构VM3的结果如图6所示。在这种情况下,我们计算图4中JC对VCE曲线的导数,得到

在图6中,我们还报告了一个参考gout_norm_MAX,对应于图5中所示的gout_MAX。很明显,与VM晶体管的行为相比,测试结构HL1可以改进SOA规范。减小声发射的试验结构可以进一步改善这一参数。

IV.热特性

对于VM晶体管的热行为,我们参考图7,我们在图7中描绘了分布在VM测试结构中的热阻。由于电流密度大,电场强,

图6测量了结构HL的gout_norm和VCE的关系。VBE = 0.875 V

图7分布在BEOL上的Rth的示意图。在这个简化的表示中,只显示了六层金属。

基极集电极空间电荷区可作为热源进行建模。热实际上对晶片的后面要么向下流动,或者向上传达,它会找到一个优惠通过金属化路径,由于铜的高导热系数比二氧化硅(参见表1)。它已被证明在[18]利用TCAD仿真,在一定的横向距离金属栈结构提供了一个等温轮廓等于环境温度。出于这个原因,添加金属栈结果添加

剩余内容已隐藏,支付完成后下载完整资料

资料编号:[608904],资料为PDF文档或Word文档,PDF文档可免费转换为Word

课题毕业论文、文献综述、任务书、外文翻译、程序设计、图纸设计等资料可联系客服协助查找。